Je vais tenter de reprendre et traduire quelques articles de Gustavo Duarte que j’ai trouvé très intéressants et concis sur le fonctionnement d’un ordinateur, de l’architecture des chipsets au fonctionnement d’un système d’exploitation. Ca risque de prendre un peu de temps, car je fais ça sur mon temps libre, mais je pense que ça peut intéresser pas mal de personnes.

L’architecture d’une carte mère moderne

Pour commencer examinons le cablage d’une carte mère d’un PC Intel actuel.

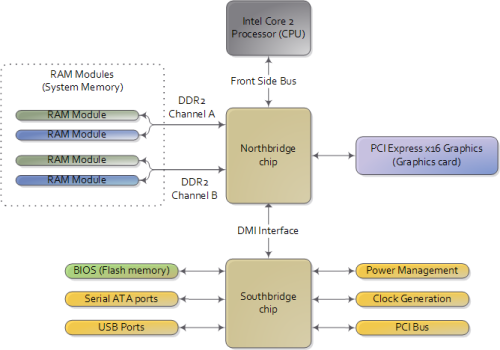

Les composants principaux de la carte apparaissent sur le schéma suivant :

En regardant ce diagramme, la chose importante à noter est que le processeur (CPU) n’a aucune idée de ce à quoi il est connecté. Il communique avec l’extérieur à l’aide de ses connecteurs mais il se fiche de savoir de quoi est fait le monde extérieur. Il peut être attaché à une carte mère dans un ordinateur mais aussi un grille pain, un routeur réseau, un implant neuronal ou un banc de test processeur.

Il y a trois moyens par lesquels le processeur peut communiquer avec l’extérieur : l’espace d’adressage mémoire, l’espace d’adressage I/O (entrées/sorties) et les interruptions. Nous allons nous intéresser seulement à la mémoire pour l’instant.

Les accès mémoire

Sur une carte mère, le canal de communication du CPU vers le monde extérieur est le front-side bus le reliant au northbridge. Quand le processeur veut lire ou écrire dans la mémoire, il le fait par ce bus.

Il utilise une partie de ces connecteurs pour transmettre l’adresse mémoire qu’il veut lire ou écrire, pendant que les autres connecteurs reçoivent la valeur lue ou à écrire.

Un Intel Core 2 QX6600 a 33 pins pour transmettre l’adresse mémoire (il y a donc 233 adresses possibles) et 64 pins pour l’envoi/réception de données (les données sont donc transmises par lot de 64 bits, soit 8 octets). Le CPU peut donc accéder à 64 Go de mémoire (233 emplacements * 8 octets) bien que la majorité des chipsets ne puissent gérer que 8 Go de RAM.

Une mémoire non linéaire

Il y a une subtilité dans l’utilisation de la mémoire. Nous sommes habitué à parler de mémoire en termes de RAM, ce à quoi les programmes accèdent en permanence. Et en effet, la majorité des requêtes mémoire du processeur sont dirigées vers les modules RAM par le northbridge.

Mais pas toutes ! Les addresses mémoire sont aussi utilisées pour communiquer avec d’autres périphériques de la carte mère, parmi lesquels la carte graphique, la plupart des cartes PCI, mais aussi la mémoire flash contenant le BIOS.

Quand le northbridge reçoit une requête mémoire il doit décider de la router : RAM ? carte graphique ? Comment savoir ?

Ce routage est effectué grâce au mapping mémoire. Pour chaque région, le mapping connaît le périphérique contrôlant cette région. La majorité des addresses est mappée vers la RAM, mais quand ce n’est pas le cas, le mapping dit au chipset quel est le périphérique gérant les requêtes de ces adresses.

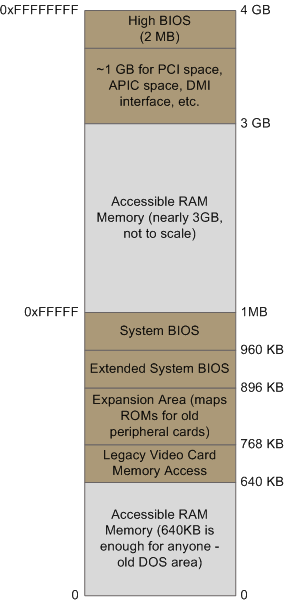

Ce mapping des adresses mémoire hors des modules RAM est la cause du « trou » historique entre les 640Ko et 1Mo de mémoire. Un trou plus important apparaît quand des adresses mémoire sont réservées à des cartes vidéo et des périphériques PCI.

C’est la raison pour laquelle les OS 32 bits ont des problèmes pour utiliser 4Go de RAM. Sous linux, le fichier virtuel /proc/iomem liste ce mapping d’adresse.

Voici un exemple de mapping typique des 4 premiers Go de mémoire d’un PC :

Les adresses mémoire réelles dépendent des périphériques et de la carte mère présents dans l’ordinateur, mais la majorité des systèmes Core 2 ont un mapping ressemblant au diagramme.

Les zones en marron sont hors-RAM. Ce sont les adresses mémoires utilisées par les bus de la carte mère.

Adresse logique ou physique

Dans le processeur, (par exemple lors de l’exécution d’un programme), les adresses mémoire sont logiques et doivent être converties en adresses physiques avant que le bus n’accède à la mémoire.

Les règles de traduction « adresse logique vers adresse physique » sont complexes et dépendent du mode dans lequel le processeur tourne (mode réel, mode protégé 32 bits, mode protégé 64 bits).

Mis à part le mécanisme de traduction, le mode du CPU détermine la quantité de mémoire physique accessible.

Par exemple, si le processeur tourne en mode 32 bits, il est capable d’accéder physiquement à 4Go de mémoire (il y a une exception appelée « physical address extension », mais ne nous en occupons pas pour l’instant).

Puisque les 1 Go d’adresses les plus élevées sont mappées vers des périphériques de la carte mère, le CPU ne peut réellement utiliser qu’environ 3 Go de RAM (parfois moins).

Si le CPU est en mode réel, il peut seulement adresser 1 Mo de RAM physique (c’était le seul mode disponible dans les premiers processeurs Intel).

Finalement, un CPU tournant en 64 bits peut adresser 64 Go (néanmoins, peu de chipsets supportent autant de RAM). En mode 64bit, il est possible d’utiliser des adresses physiques au delà du total de RAM du système pour accéder aux régions correspondantes aux adresses « volées » par les périphériques de la carte mère.

Voilà pour cet aperçu de la mémoire des PCs. Je vous donnerai plus d’informations sur le processus de démarrage d’un ordinateur dans un prochain article.

(Pour accéder à l’article original : Motherboard Chipsets and the Memory Map)

[…] Comprendre le fonctionnement des chipsets, du CPU et du mapping mémoire dans une carte mère […]